苹果造芯或失败,但每一步都在占领“芯”高地

苹果近期造芯消息不断,先有分析师爆料自研5G芯片或已失败,再有外媒报道称M2 Pro和M3芯片将使用台积电于3nm工艺制造,并预计M2 Pro将在半年后登场。

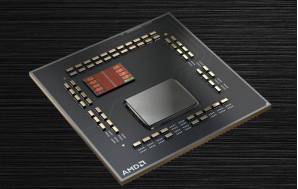

实际上苹果一直在打破规则,占领芯片圈的“时尚”高地。比如今年三月发布的M1 Ultra芯片,是由矽中介板将两颗M1 Max芯片“黏合”起来的“拼装货”,有媒体称之为“胶水芯片”。但这样的一个“胶水芯片”,里面却能满载1140 亿个晶体管,封装在逾百颗用于处理讯号、图像和人工智慧的处理器,并支援高达128GB 的统一记忆体,被誉为苹果至今最强大芯片,甚至号称可能“为摩尔定律续命”。

"胶水芯片”是什么?

实际上,“胶水芯片”的概念已有二十几年的历史。简单来讲,就是类似于用胶水将芯片连接起来而形成的模型,在业内被称Chiplet(可译为芯粒、小芯片)模型,将原先生产好的芯片集成到一个封装中,达到减少产品开发时间和成本的目的,这些芯片模块可以是不同工艺节点,最终通过裸片对裸片的方式连接在一起,还能让芯片设计成本减少一半。

虽然众多企业早已用到这个技术,比如AMD的EYPC系列CPU和线程撕裂者,Intel 的 12 代酷睿等等,但由于此前业内对于“胶水芯片”没有统一标准,大小公司都尚未往前多迈一步。

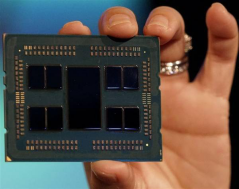

图:依次为AMD的EYPC系列CPU、线程撕裂者

直到今年3月,Intel、AMD、ARM、Google Cloud、Meta(Facebook)、微软、高通、三星、台积电等联合宣布成立小芯片联盟,并且将推出一个全新的通用小芯片互连标准:通用小芯片快连(UCle)。此后不久的5月,AMD更是宣布全面导入Chiplet 技术,还将由台积电独家代工。这才意味能够实现芯片互连的“万能胶”雏形初现。

苹果似乎虽无意加入该联盟,当业内在建立UCIe标准规格时,苹果已用行动印证了这一趋势,且产品却远远超出同行标准,确实已稳居芯片圈的“时尚”高地。

苹果走的这条路对一些芯片厂商说,也是在给他们的未来打样,芯片厂商或将陆续把视野落到多芯集成的先进封装上。

苹果的“胶水芯片”强在哪?

史无前例的架构,性能超越同行4倍多

M1 Ultra芯片使用了史无前例的UltraFusion架构,用硅中介层(Silicon Interposer)和微型凸块(Micro-Bump),将芯片连接到超过10,000个信号。

该技术提供2.5TB/s的超高处理器间带宽,以及低延迟。这一性能是其他多芯片互连技术带宽的4倍多。这个速率带宽也明显领先于英特尔、AMD等行业巨头组成的通用芯粒互连联盟(UCIe)当前的性能。

从M1 Ultra发布的UltraFusion图示,以及苹果及其代工厂(台积电)的公开专利和论文来看,UltraFusion应是基于台积电第五代CoWoS Chiplet技术的互连架构。

苹果公司Chiplet专利与M1 Ultra(参考专利US 20220013504A1)

在UltraFusion技术中,通过使用裸片缝合(Die Stitching)技术,可将4个掩模版拼接来扩大中介层的面积。在这种方法中,4个掩模被同时曝光,并在单个芯片中生成四个缝合的“边缘”。

UltraFusion架构互连技术(单层与多层,参考专利US 20220013504A1/US 20210217702A1)

这种架构能让M1 Ultra 在工作时依然表现出一枚芯片的整体性,也会被所有软件识别为一枚完整芯片,开发者无需重写代码就能直接运用它的强大性能,这在史上从无先例。

UltraFusion是苹果将两个M1 Max裸片链接的方法,这是业界2.5D芯片封装的最新范例。借助 UltraFusion,苹果能够在两个M1 Max芯片之间提供2.5TB/秒带宽。苹果已成为第一家将两个GPU绑定在一起并拥有如此大量带宽的供应商。这使他们能够尝试将两个GPU 作为单个设备呈现给操作系统和应用程序,因为它允许他们根据需要在GPU之间快速移动数据。

但实际上,苹果从M1芯片开始就已经采用2.5D封装,将内存直接封装到处理旁边,不需要PCB连线。

世界上最好的芯片都是用一种方式制造出来的,而且这种革命不会停止。另一个非常好的高级封装的好例子是Nvidia的新款A100。再次注意到PCB上没有电线。

现在:“胶水芯片”与先进封装热度持续升温

由于晶体管已经很难再缩小,而且把单一芯片越做越大也不是理想的做法,晶圆公司纷纷开始用组装的方式以提高芯片的性能。作为延续摩尔定律的重要途径之一,先进封装技术受到了业内的重视。包括代工厂、基板/PCB供应商、EMS/ODM等不同商业模式的厂商们纷纷加入战局。除了2.5D封装(interposer,RDL等),3D封装(TSV),先进封装还包括倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelackage)等技术。

先进封装已被广泛应用于计算机、通信、消费类电子、医疗、航空航天等领域,推动着封装技术以及整个电子行业向前发展。目前,倒装芯片、2.5D封装、3D封装主要用于存储器、中央处理器(CPU)、图像处理器(GPU)等;圆片级封装主要应用于功率放大器、无线连接器件、射频收发器等。

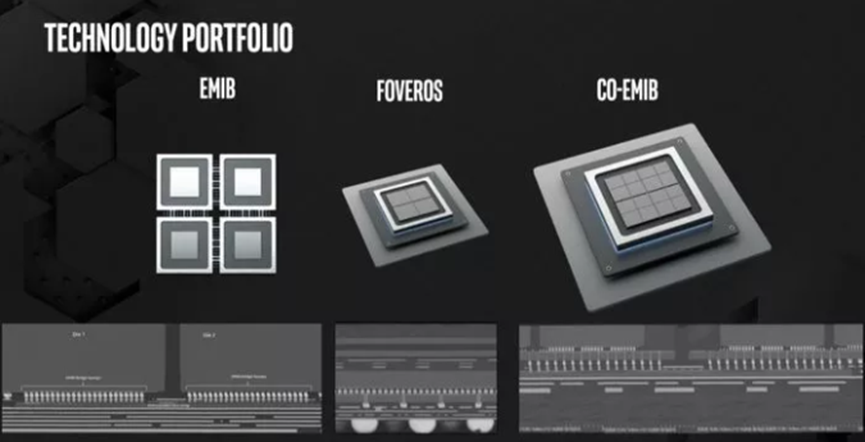

今年3月以来,先进封装似乎也迎来上升期。每个开发相关技术的公司都将自己的技术独立命名注册商标,如台积电的InFO、CoWoS,日月光的FoCoS,Amkor的SLIM、SWIFT等。

相比传统封装,一方面,先进封装技术效率高;另一方面随着芯片向着更小、更薄方向演进,先进封装技术均摊成本更低,可实现更好的性价比。

国内方面,今年4月华为也公布了新型芯片堆叠专利,从先进封装方向撕开突破口。华为的轮值董事郭平曾表示:“解决芯片问题是一个复杂的漫长过程需要有耐心,未来我们的芯片方案可能采用多核结构,以提升芯片性能。”还表示,用芯片堆叠技术以面积换性能,用不那么先进的工艺获得更强的性能,确保华为的产品具有竞争力,如此可以说是正式确认了华为正在推进芯片堆叠技术。

不仅如此,为了加强国产Chiplet技术标准的应用和推广,以及跟国际标准之间的兼容,我国早在2020年就在中科院姚期智院士的指导下成立了自己的 Chiplet 产业联盟。

总的来看,先进封装正在成为2D摩尔定律时代的晶体管缩放替代路线,目前已是半导体中越来越普遍的主题。

未来:产品大量落地,异构集成也是“未来之选”

Ml Ultra这款“胶水芯片”只是前奏,这也预示着也许未来在消费级领域,高性能产品走Chiplet这条路可以走得通。

华封科技联合创始人王宏波曾分析,2022年将是先进封装的爆发年,已经普及的先进封装工艺如FC倒装将继续蓬勃发展,中国大陆将是主战场;目前在国际上应用比较少的晶圆级封装将首先在中国台湾、韩国等海外市场迎来黄金发展期并进行大量的扩产,而大陆市场也将加快追赶的脚步,在技术上迎头赶上,从研发阶段逐步进入到小批量量产阶段;先进封装工艺也将继续开枝散叶,各种新的先进封装工艺将被研发出来,3D、ChipLet、SiP 各种方向新工艺将层出不穷、百花齐放。

此外,封装技术的发展也离不开异构集成技术,异构集成的特点很突出。一是它可以融合不同半导体材料、工艺、结构和元器件;二是采用系统设计理念;三是应用先进技术比如IP和小芯片(Chiplet),具有2.5维或3维高密度结构。因而使得异构集成芯片可以实现强大且复杂的功能,突破单一半导体工艺的性能极限;同时具有灵活性强、可靠性高、研发周期短,可实现小型化、轻质化等特点。

不仅仅是英特尔与AMD,国际芯片龙头厂商包括英伟达、高通、赛灵思等都对异构集成技术非常重视。国内方面,紫光展锐、北京君正、中星微电子等企业也在积极展开对异构集成的研究与开发,并推出相关产品与解决方案。紫光展锐新推出的唐古拉T770就集成了4核ARM A76、4核ARM A55、Mali-G57GPU以及基带芯片等,是异构集成的典型应用。

异构集成和先进封装技术扮演了关键角色,可以快速达到异构计算系统芯片所需要的功耗体积和性能要求,或许10年以后大家去买芯片,可能买的都是没有封装的小芯片,再加上异构集成这个技术进行封装。

通过先进封装技术也能够更好地提高芯片内集成密度,并且灵活度高、发展空间大。随着对算力的更高需求和封装技术的快速发展,封装技术“拐点”已至未来,物联网、汽车电子和高性能计算等新兴应用有望持续打开先进封装的成长空间。

- 成交数 --

- 成交额 --

- 应答率